Bell Road, Clement Town Dehradun-248002 Uttarakhand Ph. : 0135-2644183, 2642799, Fax : 0135-2644025 www.geu.ac.in

Department of Electronics and Communication Engineering

Master of Technology

Electronics and Communication Engineering

VLSI Design and Systems

Curriculum

# University Vision

We visualize Graphic Era (Deemed to be University) as an internationally recognized, enquiry driven, ethically engaged diverse community, whose members work collaboratively for positive transformation in the world, through leadership in teaching, research and social action.

# **University Mission**

The mission of the university is to promote learning in true spirit and offering knowledge and skills in order to succeed as professionals. The university aims to distinguish itself as a diverse, socially responsible learning community with a high-quality scholarship and academic rigor.

# **Department Vision**

The Department visualizes itself to become leading centre of learning in the field of Electronics & Communication Engineering with academic excellence in research to produce self-motivated, creative, and socially responsible engineers and specialists, ready to take up challenges of industrial development with ethics and societal commitment.

# **Department** Mission

**M1:** To provide high quality contemporary education in the field of Electronics & Communication Engineering and professional ethics to its learners.

*M2:* To provide creative learning environment for the students to equip them with strong foundation for continuing higher education.

*M3:* To pursue research and develop insight knowledge of current and emerging technologies in Electronics & Communication Engineering to serve the needs of the society, industry, and scientific community.

*M4:* To prepare students to have creative and innovative thinking to develop them into socially responsible professionals

| Graphic Era<br>Deemed to be<br>University<br>DEHRADUN | RAACA+<br>ACCREDITED |

|-------------------------------------------------------|----------------------|

|-------------------------------------------------------|----------------------|

| Progra       | <b>Program Educational Objectives (PEOs):</b>                                                                                                                         |  |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <b>PEO</b> 1 | Implementation of core-engineering knowledge to solve practical problems in the areas of VLSI design and Systems, and to produce innovative systems in these domains. |  |  |  |  |  |  |  |

| <b>PEO 2</b> | Motivating entrepreneurship in VLSI domains by integration of sustainability with efficiently designed systems.                                                       |  |  |  |  |  |  |  |

| <b>PEO 3</b> | Sharpening the educational, and research-oriented skills of the students for their easy merger into a future career in research or academia.                          |  |  |  |  |  |  |  |

| PEO 4        | Developing the design engineers with excellent ability to communicate, along with a morally responsible behavior.                                                     |  |  |  |  |  |  |  |

Bell Road,Clement Town Dehradun-248002 Uttarakhand Ph. : 0135-2644183, 2642799, Fax : 0135-2644025 www.geu.ac.in

| Program     | Outcomes (POs):                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| <b>PO1</b>  | Apply the knowledge of science, mathematics, and engineering principles for developing problem solving attitude.                 |

| <i>PO2</i>  | Identify, formulate, and solve engineering problems in the broad areas like<br>System Design using VLSI.                         |

| РО3         | Use different modern engineering software tools in the domain of VLSI and Systems Design.                                        |

| <b>PO</b> 4 | Design and conduct experiments, analyze and interpret data, imbibe programming skills for development of simulation experiments. |

| <i>PO5</i>  | Function as a member of a multidisciplinary team with sense of ethics, integrity, and social responsibility.                     |

| <b>PO6</b>  | Realize the need for self-education and ability for independent and life-long learning.                                          |

| Program Specific outcomes (PSOs): |                                                                                                         |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PSO1                              | Attain competency in areas of IC designing, testing, and developing prototype of various VLSI circuits. |  |  |  |  |  |

| PSO2                              | Integrating various VLSI sub-systems to design industrial circuits.                                     |  |  |  |  |  |

| PSO3                              | Students gain skills in developing various complicated circuits and excel in industrial sector.         |  |  |  |  |  |

## **Department of Electronics and Communication Engineering**

### **Course Components of Postgraduate Programme**

### **Definition of Credits**

|           | 1 Hr. Lecture (L) per week                                                                                                          | 1 credit     |                                                                 |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------|--|--|--|--|

|           | 1 Hr. Tutorial (T) per week                                                                                                         | 1 credit     |                                                                 |  |  |  |  |

|           | 1 Hr. Practical (P) per week                                                                                                        | 0.5          | credit                                                          |  |  |  |  |

|           | 2 Hours Practical (P) per week                                                                                                      | 1 0          | credit                                                          |  |  |  |  |

| S.<br>No. | Category                                                                                                                            | Abbreviation | Break-up of<br>credits (M. Tech-<br>VLSI Design and<br>Systems) |  |  |  |  |

| 1.        | Program Core                                                                                                                        | РС           | 34                                                              |  |  |  |  |

| 2.        | <b>Program Elective courses relevant to chosen</b><br>specialization/branch                                                         | PE           | 09                                                              |  |  |  |  |

| 3.        | Open subjects–Electives from other technical and/or emerging subjects                                                               | OE           | 03                                                              |  |  |  |  |

| 4.        | Project work, seminar and internship in<br>industry or appropriate workplace/ academic<br>and research institutions in India/abroad | PROJ         | 28                                                              |  |  |  |  |

| 5.        | General Proficiency*                                                                                                                | GP           | 04                                                              |  |  |  |  |

|           | 1                                                                                                                                   | Total        | 78                                                              |  |  |  |  |

\*Institution Initiative

Bell Road,Clement Town Dehradun-248002 Uttarakhand Ph. : 0135-2644183, 2642799, Fax : 0135-2644025 www.geu.ac.in

## **Program Course Structure (All Semesters)**

M. Tech (VLSI Design and Systems)

(Batch 2023 onwards)

#### Semester I

|        | Course Module |                                        |           |         | Te | eachii | ng |     | Weig | htage  | •     |

|--------|---------------|----------------------------------------|-----------|---------|----|--------|----|-----|------|--------|-------|

|        |               | COURSE                                 |           |         |    | Period | 0  |     |      | uation |       |

| S. No. | Code          | Course title                           | Component | Credits | L  | Т      | Р  | CIE | MSE  | SEE    | Total |

| 1      | VDM<br>101    | Semiconductor<br>Materials and Devices | РС        | 3       | 3  | 0      | 0  | 25  | 25   | 50     | 100   |

| 2      | VDM<br>102    | CMOS Analog Circuit<br>Design          | РС        | 3       | 3  | 0      | 0  | 25  | 25   | 50     | 100   |

| 3      | VDM<br>103    | Advanced Digital<br>Integrated Circuit | РС        | 3       | 3  | 0      | 0  | 25  | 25   | 50     | 100   |

| 4      | VDM<br>104    | VLSI Technology                        | РС        | 3       | 3  | 0      | 0  | 25  | 25   | 50     | 100   |

| 5      | VDM<br>-      | Program Elective-I                     | PE        | 3       | 3  | 0      | 0  | 25  | 25   | 50     | 100   |

|        |               | Laboratory and Others                  |           |         |    |        |    |     |      |        |       |

| 6      | VDM<br>151    | CMOS Analog Circuit<br>Design Lab      | РС        | 2       | 0  | 0      | 4  | 25  | 25   | 50     | 100   |

| 7      | VDM<br>152    | Digital VLSI Circuit<br>Design Lab     | РС        | 2       | 0  | 0      | 4  | 25  | 25   | 50     | 100   |

| 8      | GP101         | General Proficiency                    | GP        | 1       | 0  | 0      | 0  | 0   | 0    | 100    | 100   |

|        |               | TOTAL                                  |           | 20      | 15 | 00     | 08 |     |      |        | 800   |

#### M. Tech (VLSI Design and Systems)

(Batch 2023 onwards)

#### Semester II

| Course Module |            |                                               |           | Te      | eachii | ng     |    | Weig | htage      | :   |       |

|---------------|------------|-----------------------------------------------|-----------|---------|--------|--------|----|------|------------|-----|-------|

|               |            | COURSE                                        |           |         |        | Perioa |    |      | Evaluation |     |       |

| S. No.        | Code       | Course title                                  | Component | Credits | L      | Т      | Р  | CIE  | MSE        | SEE | Total |

| 1             | VDM<br>201 | Advanced ASIC<br>and FPGA Design              | РС        | 3       | 3      | 0      | 0  | 25   | 25         | 50  | 100   |

| 2             | VDM<br>202 | Digital System<br>Design using<br>Verilog HDL | РС        | 3       | 3      | 0      | 0  | 25   | 25         | 50  | 100   |

| 3             | VDM<br>203 | Advanced VLSI<br>Circuit Testing              | РС        | 3       | 3      | 0      | 0  | 25   | 25         | 50  | 100   |

| 4             | VDM<br>204 | Low Power VLSI<br>Design                      | РС        | 3       | 3      | 0      | 0  | 25   | 25         | 50  | 100   |

| 5             | VDM        | Program Elective-<br>II                       | PE        | 3       | 3      | 0      | 0  | 25   | 25         | 50  | 100   |

|               |            | Laboratory and Oth                            | ers       |         |        |        |    |      |            |     |       |

| 6             | VDM<br>251 | Verilog HDL Lab                               | РС        | 2       | 0      | 0      | 4  | 25   | 25         | 50  | 100   |

| 7             | VDM<br>252 | VLSI Physical<br>Design Lab                   | РС        | 2       | 0      | 0      | 4  | 25   | 25         | 50  | 100   |

| 8             | VDM<br>253 | Mini Project with<br>Seminar                  | PROJ      | 2       | 0      | 0      | 4  | 25   | 0          | 75  | 100   |

| 9             | GP<br>201  | General<br>Proficiency                        | GP        | 1       | 0      | 0      | 0  | 0    | 0          | 100 | 100   |

|               |            | TOTAL                                         |           | 22      | 15     | 00     | 12 |      |            |     | 900   |

#### M. Tech (VLSI Design and Systems)

(Batch 2023 onwards)

Semester III

| Course Module |            |                                 | Т         | eachir               | ıg |    | <b>1</b> / | F        | <b>I</b> (• |     |       |

|---------------|------------|---------------------------------|-----------|----------------------|----|----|------------|----------|-------------|-----|-------|

|               |            | COURSE                          |           | Periods Weightage: E |    |    | e: Eva     | aluation |             |     |       |

| S. No.        | Code       | Course title                    | Component | Credits              | L  | Т  | Р          | CIE      | MSE         | SEE | Total |

| 1             | VDM        | Program Elective-<br>III        | PE        | 3                    | 3  | 0  | 0          | 25       | 25          | 50  | 100   |

| 2             | VOM        | <b>Open Elective</b>            | OE        | 3                    | 3  | 0  | 0          | 25       | 25          | 50  | 100   |

|               |            | Laboratory and Oth              | ers       |                      |    |    |            |          |             |     |       |

| 3             | VDM<br>351 | Modelling and<br>Simulation Lab | РС        | 2                    | 0  | 0  | 4          | 25       | 25          | 50  | 100   |

| 4             | VDM<br>301 | Dissertation<br>Phase-I*        | PROJ      | 10                   | 0  | 0  | 20         | 25       | 50          | 125 | 200   |

| 5             | GP<br>301  | General<br>Proficiency          | GP        | 1                    | 0  | 0  | 0          | 0        | 0           | 100 | 100   |

|               |            | TOTAL                           |           | 19                   | 06 | 00 | 24         |          |             |     | 600   |

\*Students going for Industrial Project/Thesis will complete these courses through MOOCs.

Bell Road,Clement Town Dehradun-248002 Uttarakhand Ph. : 0135-2644183, 2642799, Fax : 0135-2644025 www.geu.ac.in

#### M. Tech (VLSI Design and Systems)

(Batch 2023 onwards)

Semester IV

|        | COURSE     |                          |           | Teaching<br>Periods |    |    | Weightage: Evaluation |     |     |     |       |

|--------|------------|--------------------------|-----------|---------------------|----|----|-----------------------|-----|-----|-----|-------|

| S. No. | Code       | Course title             | Component | Credits             | L  | Т  | Р                     | CIE | MSE | SEE | Total |

| 1      | VDM<br>401 | Dissertation<br>Phase-II | PROJ      | 16                  | 0  | 0  | 32                    | 50  | 100 | 250 | 400   |

| 2      | GP<br>401  | General<br>Proficiency   | GP        | 1                   | 0  | 0  | 0                     | 0   | 0   | 100 | 100   |

|        |            | TOTAL                    |           | 17                  | 00 | 00 | 32                    |     |     |     | 500   |

Bell Road,Clement Town Dehradun-248002 Uttarakhand Ph. : 0135-2644183, 2642799, Fax : 0135-2644025 www.geu.ac.in

M. Tech (VLSI Design and Systems) (Batch 2023 onwards) Program Electives and Open Electives

|                | <b>Program Elective Courses</b>                          |          |  |  |  |  |

|----------------|----------------------------------------------------------|----------|--|--|--|--|

| Course<br>Code | Course Name                                              | Semester |  |  |  |  |

|                | <b>Program Elective I</b>                                |          |  |  |  |  |

| VDM 191        | Advanced Nanotechnology                                  |          |  |  |  |  |

| VDM 192        | <b>Optimization Techniques in VLSI Design</b>            |          |  |  |  |  |

| VDM 193        | Theory and Application of Embedded Systems               |          |  |  |  |  |

| VDM 194        | Digital Signal Processing for VLSI                       | First    |  |  |  |  |

| VDM 195        | Robust Control System                                    |          |  |  |  |  |

| <i>VDM 196</i> | Control of Advanced Electric Machine                     |          |  |  |  |  |

|                | <b>Program Elective II</b>                               |          |  |  |  |  |

| VDM 291        | Micro-Sensors and MEMS                                   |          |  |  |  |  |

| VDM 292        | <b>RF</b> Microelectronics Devices                       |          |  |  |  |  |

| VDM 293        | VLSI Circuits for Biomedical Application                 |          |  |  |  |  |

| VDM 294        | Microwave & MM-wave Integrated Circuits and Applications | Second   |  |  |  |  |

| VDM 295        | Renewable Energy Resources and Energy Management         |          |  |  |  |  |

| VDM 296        | Multivariable Control System                             | -        |  |  |  |  |

|                | <b>Program Elective III</b>                              |          |  |  |  |  |

| VDM 391        | Organic Electronics Devices and Circuits                 |          |  |  |  |  |

| VDM 392        | Memory Design and Testing                                |          |  |  |  |  |

| VDM 393        | System on Chip Design and Testing                        | Third    |  |  |  |  |

| VDM 394        | VLSI Physical Design Automation                          |          |  |  |  |  |

| <i>VDM 395</i> | Power Quality Assessment                                 |          |  |  |  |  |

| <i>VDM 396</i> | <b>Optimal &amp; Adaptive Control</b>                    |          |  |  |  |  |

|                | <b>Open Elective Courses</b>               |                 |  |  |  |  |  |

|----------------|--------------------------------------------|-----------------|--|--|--|--|--|

| Course<br>Code | Course Name                                | Semester        |  |  |  |  |  |

| VOM 301        | Cloud Computing                            |                 |  |  |  |  |  |

| VOM 302        | Internet of Things                         | <i>T</i> T1 • 1 |  |  |  |  |  |

| VOM 303        | Artificial Intelligence and expert systems | Third           |  |  |  |  |  |

| VOM 304        | Soft Computing                             |                 |  |  |  |  |  |

| Allenaviat     |                                            | -               |  |  |  |  |  |

#### Abbreviations:

| L    | Lecture               |

|------|-----------------------|

| Τ    | Tutorial              |

| Р    | Practical             |

| CWA  | Class Work Assessment |

| MSE  | Mid Semester Exam     |

| ESE  | End Semester Exam     |

| PC   | Program Core          |

| PE   | Program Elective      |

| OE   | Open Elective         |

| PROJ | Project               |

| GP   | General Proficiency*  |

\*Institution Initiative

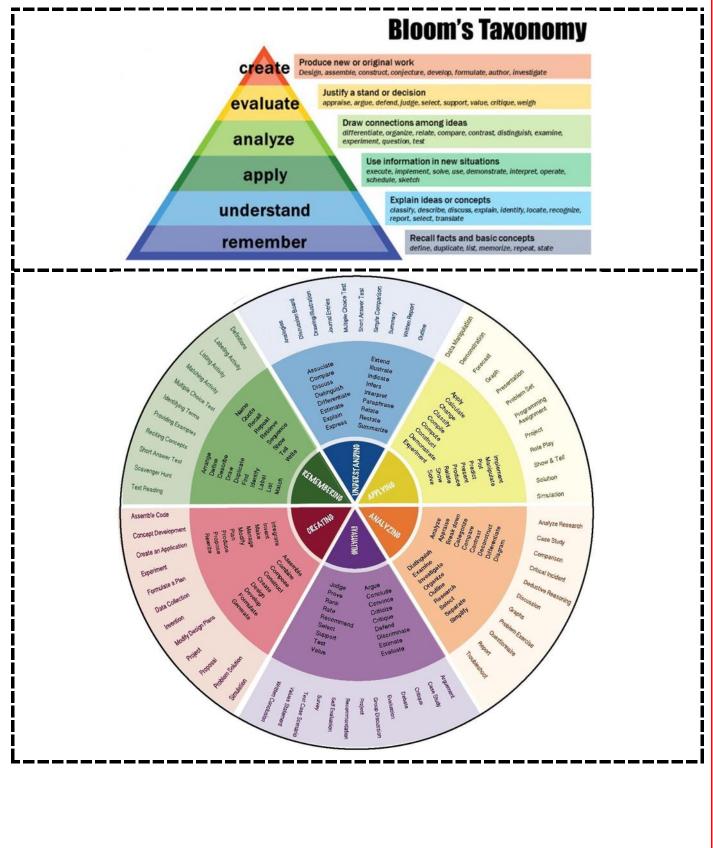

## **Bloom's Taxonomy for Curriculum Design and Assessment**

Preamble

The design of curriculum and assessment is based on Bloom's Taxonomy. A comprehensive guideline for using Bloom's Taxonomy is given below for reference.

|               |                                                         | SEM                                                                                       | ESTER I |             |         |                       |              |

|---------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|-------------|---------|-----------------------|--------------|

| <b>S.</b> No. | Department of Electronics and Communication Engineering |                                                                                           |         |             |         |                       |              |

| 1.            | Subject Code                                            | VDM 101                                                                                   | C       | ourse Title | Semicor | nductor Ma<br>Devices | iterials and |

| 2.            | <b>Contact Hours</b>                                    | L                                                                                         | 3       | Т           | 0       | Р                     | 0            |

| 3.            | Examination<br>Duration                                 | Theory                                                                                    |         | 3           | Practi  | cal                   | 0            |

| 4.            | Relative Weight                                         | CIE                                                                                       | 25      | MSE         | 25      | SEE                   | 50           |

| 6.            | Credit                                                  |                                                                                           |         | 6           | )3      |                       |              |

| 6.            | Semester                                                |                                                                                           |         | Fi          | irst    |                       |              |

| 7.            | Category of Course                                      | РС                                                                                        |         |             |         |                       |              |

| 8.            | Pre-requisite                                           | Basic Electronics Engineering (TEC-101/201), Electronic Devices<br>and Circuits (TEC-301) |         |             |         |                       |              |

| 9. | Course Outcomes | After completion of the course the students will be able to:<br>CO1: <b>Create</b> basic understanding of semiconductor device physics.<br>CO2: <b>Evaluate</b> two terminal MOS structure in terms of its electrical<br>parameters.                                                                                                                            |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                 | CO3: Analyse the three terminal MOS structure in terms of electrical potential<br>and charge.<br>CO4: Apply surface potential and charges in different regions of MOSFET<br>operation.<br>CO5: Understand the short channel and narrow channel effects.<br>CO6: Implement the concepts of semiconductor device physics in developing<br>real life applications. |

| <i>S. No.</i> | Contents                                                                                                                                                                                                                                                                                                                | <b>Contact Hours</b> |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.            | Unit 1: Basics of Semiconductors:<br>Semiconductor materials, Energy levels, Intrinsic and extrinsic semiconductor,<br>Equilibrium in absence/presence of electric field.                                                                                                                                               | 8                    |

| 2.            | <b>Unit 2: PN Junction Diode:</b><br>Junction diode: PN junction, Tunnel diode, Quasi-fermi levels, Depletion width capacitance and its application in doping profile determination, I-V characteristics of narrow and wide base diodes and their equivalent circuits, Breakdown mechanisms, Small signal ac impedance. | 0                    |

| 3.            | Unit 3: Two Terminal MOS Structure:                                                                                                                                                                                                                                                                                     | 10                   |

|    | Flat band voltage, Potential balance and charge balance, Effect of gate body voltage on surface condition, Accumulation, Depletion, Inversion, General analysis, Small signal capacitance.                                                                                                                      |    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4. | Unit 4: Three Terminal MOS Structure:<br>Contacting the inversion layer, Body effect, Different regions of operation, Pinch-off<br>voltage.                                                                                                                                                                     | 10 |

| 5. | Unit 5: Four Terminal MOS Structure:<br>Transistors regions of operation, Complete all-region model, Simplified all-region model,<br>Models based on quasi fermi potential, Regions of inversion in terms of terminal voltage,<br>Temperature effects, Breakdown, Enhancement mode, Depletion mode transistors. | 6  |

|    | Total                                                                                                                                                                                                                                                                                                           | 42 |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                                                                               | Edition         | Year of<br>Publication /<br>Reprint |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|

|           | Textbooks                                                                                                                                                                      |                 |                                     |

| 1.        | <i>Tsividis, Yannis, and Colin McAndrew, "Operation and Modelling of the</i><br><i>MOS Transistor", Oxford: Oxford University Press, Vol. 2, 3<sup>rd</sup> Edition, 2003.</i> | 3 <sup>rd</sup> | 2003                                |

| 2.        | S. Kang and Y. Leblebici, "CMOS Digital Integrated Circuits, Analysis and Design", 3 <sup>rd</sup> Edition, Tata McGraw-Hill, 2003.                                            | 3 <sup>rd</sup> | 2003                                |

|           | Reference Books                                                                                                                                                                |                 |                                     |

| 1.        | Adel S. Sedra, Kenneth C. Smith, " Microelectronic Circuits", Oxford<br>University Press                                                                                       | $7^h$           | 2014                                |

| 2.        | S. Salivahanan and S. Arivazhagan, "Digital Circuits and Design", Oxford<br>University Press,                                                                                  | 5 <sup>th</sup> | 2008                                |

| 3.        | Robert L. Boylestad and Louis Nashelsky, "Electronic Devices and Circuit<br>Theory", Prentice Hall of India (PHI).                                                             | $9^{th}$        | 2006                                |

| 12. | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-----|--------------------|----------------------------------------------------------|

|     |                    |                                                          |

|               |                                                                | SE    | MEST                                       | ER I |            |         |            |             |

|---------------|----------------------------------------------------------------|-------|--------------------------------------------|------|------------|---------|------------|-------------|

| <i>S. No.</i> | <b>Department of Electronics and Communication Engineering</b> |       |                                            |      |            |         |            |             |

| 1.            | Subject Code                                                   | VDM 1 | 02                                         | Co   | urse Title | CMOS A  | Analog Cir | cuit Design |

| 2.            | Contact Hours                                                  | L     | 3                                          |      | Т          | 0       | Р          | 0           |

| 3.            | Examination<br>Duration                                        | Theor | y                                          |      | 3          | Practio | cal        | 0           |

| 4.            | Relative Weight                                                | CIE   | 2.                                         | 5    | MSE        | 25      | SEE        | 50          |

| 6.            | Credit                                                         | 03    |                                            |      |            |         |            |             |

| 6.            | Semester                                                       | First |                                            |      |            |         |            |             |

| 7.            | Category of Course                                             | РС    |                                            |      |            |         |            |             |

| 8.            | Pre-requisite                                                  |       | Electronics Devices and Circuits (TEC 301) |      |            |         |            |             |

| 9. Course Outcom | CO1: <b>Recall</b> the knowledge of analog IC design in CMOS technologies.                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <ul> <li>CO2: Understand MOS transistors with different configurations.</li> <li>CO3: Apply the concepts of multistage and differential MOS amplifiers.</li> <li>CO4: Analyse the current mirror circuits.</li> <li>CO5: Assess and evaluation the feedback amplifiers and phase locked loop.</li> <li>CO6: Design and develop various CMOS analog circuits.</li> </ul> |

| <i>S. No</i> . | Contents                                                                                                                                                                                                                                                                                                                                       | Contact Hours |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.             | Unit 1: Models for Integrated Circuit Active Devices:<br>The depletion region of a PN junction, Depletion region capacitance and junction<br>breakdown, Basics of MOS transistor, Derivation of current-voltage relationship, Analysis<br>of MOS as an amplifier, Small signal models of MOS transistor, MOS transistor frequency<br>response. | 8             |

| 2.             | Unit 2: Single Stage Amplifier:<br>Common source stage with resistive load, CS stage with diode connected load, CS stage<br>with current source load, CS stage with triode load, CS stage with source generation,<br>Source follower and common gate configuration.                                                                            | 9             |

| 3.             | Unit 3: Multistage Amplifier and Operational Amplifier:<br>Cascode current source, Cascode amplifier, Differential pair, Small and large signal<br>analysis of differential amplifier, Differential amplifier with MOS loads, OPAMP design:<br>General consideration, One stage OpAmp                                                          | 9             |

| 4.             | Unit 4: Current Mirrors, Active Loads and References:                                                                                                                                                                                                                                                                                          | 9             |

|    | Simple current mirror, Cascode current mirror, Wilson current mirror, Common source<br>amplifier with complementary load, Voltage and current references: Widlar and peaking<br>current sources, supply insensitive biasing |    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5. | Unit 5: Feedback and Non-Linear Analog Circuits:<br>General consideration, Properties of feedback circuits, Feedback configuration,<br>Nonlinear analog circuits: LC oscillators, Simple phase locked loop.                 | 9  |

|    | Total                                                                                                                                                                                                                       | 44 |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                 | Edition         | Year of<br>Publication /<br>Reprint |

|-----------|------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|

|           | Textbooks                                                                                                        |                 |                                     |

| 1.        | B. Razavi, Design of analog CMOS Integrated Circuits, McGraw-Hill                                                | $I^{st}$        | 2002                                |

| 2.        | Mohammed Ismail and Terri Faiz, Analog VLSI Signal and Information<br>Process, McGraw-Hill.                      | I <sup>st</sup> | 1994                                |

|           | Reference Books                                                                                                  |                 |                                     |

| 1.        | Paul R. Gray and R. G. Meyer, Analysis and Design of Analog Integrated<br>Circuits, John Wiley and Sons          | $4^{th}$        | 2001                                |

| 2.        | R. Jacob Baker, H. W. Li, and D.E. Boyce, CMOS: Circuit Design, Layout<br>and Simulation, Prentice-Hall of India | 3 <sup>rd</sup> | 2010                                |

| <i>12</i> . | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-------------|--------------------|----------------------------------------------------------|

|             |                    |                                                          |

|        |                                                         | SE     | MEST                                                         | ER I |     |         |     |      |

|--------|---------------------------------------------------------|--------|--------------------------------------------------------------|------|-----|---------|-----|------|

| S. No. | Department of Electronics and Communication Engineering |        |                                                              |      |     |         |     |      |

| 1.     | Subject Code                                            | VDM 1  | VDM 103 Course Title Advanced Digit<br>Circu                 |      |     |         | 0   |      |

| 2.     | Contact Hours                                           | L      | Ĵ                                                            | }    | Т   | 0       | P   | 0    |

| 3.     | Examination<br>Duration                                 | Theory | V                                                            |      | 3   | Practio | cal | 0    |

| 4.     | Relative Weight                                         | CIE    | 2                                                            | 5    | MSE | 25      | SE  | E 50 |

| 6.     | Credit                                                  |        | 03                                                           |      |     |         |     |      |

| 6.     | Semester                                                |        | First                                                        |      |     |         |     |      |

| 7.     | Category of Course                                      | РС     |                                                              |      |     |         |     |      |

| 8.     | Pre-requisite                                           | Bas    | <b>Basic Electronics Engineering and Digital Electronics</b> |      |     |         |     |      |

| 9. | Course Outcomes | After completion of the course the students will be able to:<br>CO1: <b>Describe</b> the basic MOS structure and layout design<br>CO2: <b>Understand</b> the static and dynamic characteristics of MOS inverters<br>CO3: <b>Apply</b> the MOS concepts to design combinational and sequential MOS |

|----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                 | logic circuits.<br>CO4: <b>Analyze</b> different digital MOS logic circuits.                                                                                                                                                                                                                      |

|    |                 | CO5: Estimate power consumption of CMOS logic circuits.<br>CO6: Integrate various concepts of digital VLSI circuit design and apply them<br>in designing of MOS based digital circuits.                                                                                                           |

| <b>S.</b> No. | Contents                                                                                                                                                                                                                                                                                                         | Contact Hours |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.            | Unit 1: Introduction and Implementation of strategies for digital ICs:<br>Issues in Digital Integrated Circuit Design, Quality Metrics of a Digital Design, Design<br>rule: Stick diagram and layout. Custom Circuit design, Cell based, and Array based design<br>implementations.                              | 10            |

| 2.            | <i>Unit 2: MOS Inverters:</i><br><i>Static and Dynamic Characteristics of CMOS inverter, Power dissipation, Logical effort.</i>                                                                                                                                                                                  | 10            |

| 3.            | Unit 3: Designing combinational and sequential circuits:<br>Static CMOS design, Different styles of logic circuits, Logical effort of complex gates,<br>Static and dynamic properties of complex gates, Dynamic CMOS Logic. Timing metrics of<br>sequential circuits, Dynamic latches and Registers. Pipelining. | 10            |

| 4.            | Unit 4: Interconnect and Timing Issues:<br>Circuit characterization and performance estimation - Resistance, Capacitance<br>estimation - Switching characteristics - Delay models – Timing issues in Digital circuits,<br>Power dissipation. Impact of Clock Skew and Jitter.                                    | 6             |

| 5.            | Unit 5: Memory Design:                                                                                                                                                                                                                                                                                           | 6             |

|      | Read-Only Memories, ROM cells, Read-write memories (RAM), dynamic memory design, |    |

|------|----------------------------------------------------------------------------------|----|

|      | 6 transistor SRAM cell, Sense amplifiers                                         |    |

|      | Total                                                                            | 42 |

| 11 0 |                                                                                  |    |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                              | Edition | Year of<br>Publication /<br>Reprint |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------|

|           | Textbooks                                                                                                                     |         |                                     |

| 1.        | S. Kang and Y. Leblebici, "CMOS Digital Integrated Circuits, Analysis and Design", Tata McGraw-Hill.                          | 3rd     | 2003                                |

| 2.        | J. M. Rabaey, A. Chandrakasan and B. Nikolic, "Digital Integrated Circuits:<br>A Design Perspective", Prentice-Hall of India. | 2nd     | 2006                                |

|           | Reference Books                                                                                                               |         |                                     |

| 1.        | John P. Uyemura, "Introduction to VLSI Circuits", Wiley India Pvt. Ltd.                                                       | lst     | 2012                                |

| 2.        | Eugene Fabricius, "Introduction to VLSI Design", New Ed Edition, Tata<br>McGraw - Hill Education.                             | lst     | 1990                                |

| 3.        | N. H. E. Weste et. al., "CMOS VLSI Design", Pearson.                                                                          | 3rd     | 2005                                |

| 4.        | R. Jacob Baker, "CMOS: circuit design, layout, and simulation", John<br>Wiley & Sons,                                         | 3rd     | 2010                                |

| 12. | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-----|--------------------|----------------------------------------------------------|

|     |                    |                                                          |

SEMESTER I

| <i>S. No.</i> | <b>Department of Electronics and Communication Engineering</b> |                                                              |    |              |        |            |      |

|---------------|----------------------------------------------------------------|--------------------------------------------------------------|----|--------------|--------|------------|------|

| 1.            | Subject Code                                                   | VDM 1                                                        | 04 | Course Title | V      | LSI Techno | logy |

| 2.            | Contact Hours                                                  | L                                                            | 3  | Т            | 0      | Р          | 0    |

| 3.            | Examination<br>Duration                                        | Theor                                                        | v  | 3            | Practi | cal        | 0    |

| 4.            | Relative Weight                                                | CIE                                                          | 25 | MSE          | 25     | SEE        | 50   |

| 6.            | Credit                                                         | 03                                                           |    |              |        |            |      |

| 6.            | Semester                                                       | First                                                        |    |              |        |            |      |

| 7.            | Category of Course                                             | РС                                                           |    |              |        |            |      |

| 8.            | Pre-requisite                                                  | <b>Basic Electronics Engineering and Digital Electronics</b> |    |              |        |            |      |

| 9. Course Outcomes | <ul> <li>After completion of the course the students will be able to:</li> <li>CO1: Explain about wafer fabrication techniques and oxidation process</li> <li>CO2: Analyse photolithography and etching techniques of VLSI design.</li> <li>CO3: Extend the knowledge of different physical and chemical deposition methods.</li> <li>CO4: Investigate metal deposition techniques and IC fabrication methodologies.</li> <li>CO5: Design and analysis of different packaging methods.</li> <li>CO6: Create a base for the semiconductor device fabrication using VLSI technology.</li> </ul> |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>S. No.</i> | Contents                                                                                                                                                                                                                                                                                                                                                                                                            | <b>Contact Hours</b> |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.            | Unit 1: Wafer Preparation and Oxidation:<br>Electron grade silicon, Crystal growth, Wafer preparation, Processing considerations,<br>Vapor phase epitaxy and molecular beam epitaxy, Film characteristics, SOI structure,<br>Oxide formation, Kinetics, Oxidation systems, Dry and wet oxidation, Masks properties of<br>SiO2, Oxidation defects, Redistribution of dopant at interface, Oxidation of poly silicon. | 10                   |

| 2.            | Unit 2: Lithography and Etching:<br>Optical, Electron, X-Ray and Ion Lithography methods, Positive and negative photo resist.<br>Plasma properties, Size, Control, Etch mechanism, Etch techniques and equipment.                                                                                                                                                                                                   | 8                    |

| 3.            | Unit 3: Deposition and diffusion:<br>Deposition process and methods, Diffusion in solids, Diffusion equation and Diffusion<br>mechanisms, Flick's one-dimensional diffusion equation, Atomic diffusion mechanism,<br>Measurement techniques, Range theory, Implant equipment, Ion implantation, Damage<br>and annealing, Ion implantation systems.                                                                  | 8                    |

| 4.            | <b>Unit 4: Metallization and IC Fabrication:</b><br>Metallization and its applications, Process simulation of Ion implementation, Diffusion,<br>Oxidation, Epitaxy, Lithography, Etching and deposition, Annealing shallow junction –                                                                                                                                                                               | 8                    |

|    | High energy implantation, Physical vapours deposition patterning. NMOS, CMOS and bipolar IC technologies and IC fabrication. |    |

|----|------------------------------------------------------------------------------------------------------------------------------|----|

| 5. | <i>Unit 5: Packaging:</i><br>Analytical and assembly techniques and packaging of VLSI devices.                               | 8  |

|    | Total                                                                                                                        | 42 |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                             | Edition         | Year of<br>Publication /<br>Reprint |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|

|           | Textbooks                                                                                                                    |                 |                                     |

| 1.        | S. M. Sze, "VLSI Technology", McGraw Hill, 2nd Edition, 1988.                                                                | $2^{nd}$        | 1988                                |

| 2.        | W. Wolf, "Modern VLSI Design", Pearson, 3rd Edition, 2002.                                                                   | 3 <sup>rd</sup> | 2002                                |

|           | Reference Books                                                                                                              |                 |                                     |

| 1.        | S. K. Gandhi, " <b>VLSI Fabrication Principles Silicon and Gallium</b><br><b>Arsenide</b> ", Wiley-INDIA, 2nd Edition, 1994. | $2^{nd}$        | 1994                                |

| 2.        | Wai Kai Chen, "VLSI Technology", CRC press, 1st Edition, 2003.                                                               | $I^{st}$        | 2003                                |

| 12. | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-----|--------------------|----------------------------------------------------------|

|     |                    |                                                          |

|               |                         | SE                                                | MEST                                            | ER I        |             |            |          |            |  |

|---------------|-------------------------|---------------------------------------------------|-------------------------------------------------|-------------|-------------|------------|----------|------------|--|

| <i>S. No.</i> | Departn                 | nent of Electronics and Communication Engineering |                                                 |             |             |            |          |            |  |

| 1.            | Subject Code            | <b>VDM 1</b> .                                    | VDM 151 Course Title CMOS Analog Circuit Design |             |             |            |          |            |  |

| 2.            | Contact Hours           | L                                                 | l                                               | )           | Т           | 0 P        |          |            |  |

| 3.            | Examination<br>Duration | Theory 0                                          |                                                 | Practical 4 |             |            |          |            |  |

| 4.            | Relative Weight         | CIE                                               | 2                                               | 5           | MSE         | 25         | SEE      | E 50       |  |

| 6.            | Credit                  |                                                   |                                                 |             | 0           | 2          |          |            |  |

| 6.            | Semester                |                                                   |                                                 |             | Fi          | rst        |          |            |  |

| 7.            | Category of Course      | РС                                                |                                                 |             |             |            |          |            |  |

| 8.            | Pre-requisite           | Electron                                          | nics D                                          | evices      | and Circuit | t, VLSI Te | chnology | and Design |  |

| 9. | Course Outcomes | After completion of the course the students will be able to:              |

|----|-----------------|---------------------------------------------------------------------------|

|    |                 | CO1: Understand Cadence Virtuoso simulation tool.                         |

|    |                 | CO2: Design common source, common drain, and operational amplifier using  |

|    |                 | Cadence tool.                                                             |

|    |                 | CO3: Simulate and analyse various CMOS based circuits using Cadence tool. |

|    |                 | CO4: Integrate the acquired knowledge for developing CMOS based circuits. |

|    |                 |                                                                           |

| S. No. | List of problems for which student should develop program and execute in the Laboratory                                              | Contact Hours |

|--------|--------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.     | Design a new cell view and build common source amplifier and create a symbol for the common source amplifier using 90 nm technology. | 1             |

| 2.     | Simulation of common source amplifier test circuit using common source amplifier symbol using 90 nm technology.                      | 1             |

| 3.     | Create a layout of common source amplifier using 90 nm technology.                                                                   | 2             |

| 4.     | Design a new cell view and build common drain amplifier and create a symbol for the common drain amplifier using 90 nm technology.   | 1             |

| 5.     | Simulation of common drain amplifier test circuit using common drain amplifier symbol using 90 nm technology.                        | 1             |

| 6.     | Create a layout of common drain amplifier using 90 nm technology.                                                                    | 2             |

|        | Graphic Era<br>Deemed to be<br>University<br>DEHRADUN                                                                              | akhand<br>42799,<br>544025 |

|--------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 7.     | Design a new cell view and build Differential amplifier and create a symbol for the Differential amplifier using 90 nm technology. | 1                          |

| 8.     | Simulation of Differential amplifier test circuit using Differential amplifier symbol using 90 nm technology.                      | I                          |

| 9.     | Create a layout of Differential amplifier using 90 nm technology.                                                                  | 2                          |

| 10.    | Design a new cell view and build operational amplifier and create a symbol for the operational amplifier using 90 nm technology.   | I                          |

| 11.    | Simulation of operational amplifier test circuit using operational amplifier symbol using 90 nm technology.                        | 1                          |

| 12.    | Create a layout of operational Amplifier using 90 nm technology.                                                                   | 2                          |

|        | Total                                                                                                                              | 16                         |

|        | Innovative Experiments                                                                                                             |                            |

| 13.    | Design and simulation of current mirror circuits using 90 nm technology.                                                           | 2                          |

| 14     | Design and Simulation of Cascode amplifier using 90 nm technology.                                                                 | 2                          |

|        | Total                                                                                                                              | 04                         |

| 1. Sug | gested Books                                                                                                                       |                            |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                                         | Edition         | Year of<br>Publication /<br>Reprint |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|

|           | Textbooks                                                                                                                                |                 |                                     |

| 1.        | B. Razavi, Design of analog CMOS Integrated Circuits, McGraw-Hill                                                                        | $I^{st}$        | 2002                                |

| 2.        | Paul R. Gray and R. G. Meyer, Analysis and Design of Analog Integrated<br>Circuits, John Wiley and Sons                                  | $4^{th}$        | 2001                                |

| 3.        | Mohammed Ismail and Terri Faiz, Analog VLSI Signal and<br>Information Process, McGraw-Hill<br><b>Reference Books</b>                     | $I^{st}$        | 1994                                |

|           | Reference Dooks                                                                                                                          |                 |                                     |

| 1.        | <i>R. Jacob Baker, H. W. Li, and D.E. Boyce, CMOS: Circuit Design, Layout and Simulation, Prentice-Hall of India, 3rd Edition, 2010.</i> | 3 <sup>rd</sup> | 2010                                |

| 12. | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-----|--------------------|----------------------------------------------------------|

|     |                    |                                                          |

SEMESTER I

| <i>S. No.</i> | Departm                 | eent of Electronics and Communication Engineering |             |                    |         |     |    |  |  |

|---------------|-------------------------|---------------------------------------------------|-------------|--------------------|---------|-----|----|--|--|

| 1.            | Subject Code            | VDM 1                                             | LSI Circuit | Circuit Design Lab |         |     |    |  |  |

| 2.            | Contact Hours           | L                                                 | 0           | Т                  | 0       | Р   | 4  |  |  |

| 3.            | Examination<br>Duration | Theor                                             | v           | 0                  | Practio | cal | 4  |  |  |

| 4.            | Relative Weight         | CIE                                               | 25          | MSE                | 25      | SEE | 50 |  |  |

| 6.            | Credit                  |                                                   | 8           |                    | 02      |     |    |  |  |

| 6.            | Semester                |                                                   |             | F                  | First   |     |    |  |  |

| 7.            | Category of Course      | РС                                                |             |                    |         |     |    |  |  |

| 8.            | Pre-requisite           | Digital Electronics                               |             |                    |         |     |    |  |  |

| 9. | Course Outcomes | After completion of the course the students will be able to:               |

|----|-----------------|----------------------------------------------------------------------------|

|    |                 | CO1: Understand the CMOS based digital integrated circuits                 |

|    |                 | CO2: Analyze CMOS based combinational circuits using 180nmTechnology       |

|    |                 | CO3: Evaluate CMOS based sequential circuits and memory devices.           |

|    |                 | CO4: Design and validate various CMOS based digital circuits using Cadence |

|    |                 | tool                                                                       |

| <i>S. No.</i> | List of problems for which student should develop program and execute in the<br>Laboratory                   | Contact Hours |

|---------------|--------------------------------------------------------------------------------------------------------------|---------------|

| 1.            | Design and comparison of DC and transient output characteristics of CMOS inverter at different aspect ratio. | 2             |

| 2.            | Draw a layout of CMOS inverter using 45 nm technology and check for LVS and DRC for inverter circuit.        | 2             |

| 3.            | Design and implement various gates with CMOS logic along with its layout.                                    | 2             |

| 4.            | Draw a schematic of half adder/full adder using 45 nm technology and analyse its transient characteristics.  | 2             |

| 5.            | Draw the layouts of half adder/full adder using 45 nm technology and simulate its transient characteristics. | 2             |

| 6.            | Design a schematic of comparator using 45 nm technology and simulate its transient characteristics           | 2             |

| 7.            | Design and Implementation of 2:1 Multiplexer and 1:2 Demultiplexer.                                          | 2             |

| 8.  | Design the schematic of latches using 45 nm technology and simulate its transient characteristics         | 2  |

|-----|-----------------------------------------------------------------------------------------------------------|----|

| 9.  | Design the schematic of flip-flops using 45 nm technology and simulate its transient characteristics      | 2  |

| 10. | Design the schematic of shift register using 45 nm technology and simulate its transient characteristics  | 2  |

| 11. | Design the schematic of up/down counter using 45 nm technology and simulate its transient characteristics | 2  |

| 12. | Design the schematic of 6T RAM using 45 nm technology and simulate its transient characteristics          | 2  |

|     | Total                                                                                                     | 24 |

|     | Innovative Experiments                                                                                    |    |

| 13. | Design and implementation of Flash Memory with Cadence tool.                                              | 2  |

| 14. | Design and implementation of Different Analog to Digital converter (ADC) with Cadence tool.               | 2  |

| 15. | Simulate substrate bias (Body) effect in CMOS inverter.                                                   | 2  |

|     |                                                                                                           | 06 |

| <i>11</i> . | Mode of Evaluation | Test / Quiz / Assignment / Mid Term Exam / End Term Exam |

|-------------|--------------------|----------------------------------------------------------|

|             |                    |                                                          |

| <i>S. No.</i> | Department of Electronics and Communication Engineering |                                               |          |               |             |            |          |      |  |

|---------------|---------------------------------------------------------|-----------------------------------------------|----------|---------------|-------------|------------|----------|------|--|

| 1.            | Subject Code                                            | VDM 201Course TitleAdvanced ASIC an<br>Design |          |               |             |            |          |      |  |

| 2.            | Contact Hours                                           | L                                             | 3        | }             | Т           | 0          | P        | 0    |  |

| 3.            | Examination<br>Duration                                 | Theor                                         | v        | 3             |             | Practi     | cal      | 0    |  |

| 4.            | Relative Weight                                         | CIE                                           | 2.       | 5             | MSE         | 25         | SE       | E 50 |  |

| 6.            | Credit                                                  |                                               | <u>n</u> |               | 0.          | 3          | <u> </u> |      |  |

| 6.            | Semester                                                |                                               |          |               | Seco        | ond        |          |      |  |

| 7.            | Category of Course                                      | РС                                            |          |               |             |            |          |      |  |

| 8.            | Pre-requisite                                           |                                               | Ŀ        | 4 <i>dvan</i> | ced Digital | Integrated | Circuit  |      |  |

| 9. | <b>Course Outcomes</b> | After completion of the course the students will be able to:                    |

|----|------------------------|---------------------------------------------------------------------------------|

|    |                        | CO1: <b>Describe</b> the concepts of ASICs, CMOS Logic and ASIC Library Design. |

|    |                        | CO2: Understanding about partitioning, floor planning, placement and routing    |

|    |                        | including circuit extraction of ASIC.                                           |

|    |                        | CO3: Applying the concepts of ASIC and FPGA in designing various                |

|    |                        | architecture of different types of FPGA.                                        |

|    |                        | CO4: Analysis of the issues involved in ASIC design, including technology       |

|    |                        | choice, design management, tool-flow, verification, debug and test, as well as  |

|    |                        | the impact of technology scaling on ASIC design.                                |

|    |                        | CO5: Evaluation of SOC based integrated circuits for various FPGA               |

|    |                        | applications.                                                                   |

|    |                        | CO6: <b>Designing</b> of ASIC family using Xilinx tool to optimize the device   |

|    |                        | performance.                                                                    |

|    |                        | F J                                                                             |

#### 10. Details of the Course

| <i>S. No.</i> | Contents                                                                                                                                                                                                                                                                                                           | Contact Hours |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.            | Unit 1: Introduction:<br>Types of ASICs, Design flow, CMOS transistors CMOS design rules, Combinational logic<br>cell, Sequential logic cell, Transistors as resistors, Transistor parasitic capacitance,<br>Logical effort, Library cell design, Library architecture.                                            | 10            |

| 2.            | <i>Unit 2: ASIC Physical Design:</i><br><i>System partition, partitioning, partitioning methods, interconnect delay models and measurement of delay, floor planning, placement, Routing, Circuit extraction, Design Rule Check.</i>                                                                                | 9             |

| 3.            | Unit 3: FPGA Architecture:<br>Field Programmable gate arrays, Logic blocks, routing architecture, Design flow<br>technology, Xilinx XC4000, ALTERA's FLEX 8000/10000, ACTEL's ACT-1,2,3 and their<br>speed performance Case studies: Altera MAX 5000 and 7000, Altera MAX 9000, Spartan<br>II and Virtex II FPGAs. | 10            |

#### SEMESTER II

| 4. | Unit 4: Trade off issues at System Level:<br>Optimization with regard to speed, area and power, asynchronous and low power system<br>design. ASIC physical design issues, System Partitioning, Power Dissipation, Partitioning<br>Methods.                                            | 8  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5. | Unit 5: System on Chip Design:<br>Design using Xilinx Family, System on Chip Design, SoC Design Flow, Platform based<br>and IP based SoC designs, Basic Concept of Bus – Based communication architectures,<br>On- chip communication architectures standards, Low power SoC designs. | 8  |

|    | Total                                                                                                                                                                                                                                                                                 | 45 |

| S.<br>No. | Name of Authors/Books/Publishers                                                                                      | Edition         | Year of<br>Publication /<br>Reprint |

|-----------|-----------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|

|           | Textbooks                                                                                                             |                 |                                     |

| 1.        | Pasricha and N. Dutt, " <b>On-Chip Communication Architectures System on</b><br><b>Chip Interconnect</b> ", Elseveir. | 1 <sup>st</sup> | 2008                                |

| 2.        | Michael John Sebastian Smith, "Application-Specific Integrated<br>Circuits", Addison-Wesley VLSI Systems Series       | 1 <sup>st</sup> | 2008                                |

|           | Reference Books                                                                                                       |                 |                                     |

| 1.        | M. Rabaey, A. Chandrakasan, and B.Nikolic, "Digital Integrated Circuit<br>Design Perspective", Wiley.                 | 2 <sup>nd</sup> | 2003                                |